Převodník USB <-> JTAG, RS-232 (TTL)

Přidáno: 16.06.2007 Uživatel: admin

Stav konstrukce: Hotová

Základní popis

Jedná se o relativně jednoduchý převodník z USB na ladící a vývojové rozhraní JTAG (IEE1149.1).

Základem převodníku je integrovaný obvod FT2232D jež obsahuje všechny důležité části pro obsluhu

sběrnice USB a 2 univerzální výstupní bloky, které mohou realizovat rozhraní jako např. UART,

8b paralelní sběrnice či mnou použitý JTAG, SPI a I2C. Celý převodník je navržen pro vestavbu

do krabičky USET1 od firmy ASIX

Vlastnosti

- Připojení přes USB

- Podpora protokolů JTAG, SPI a I2C (případně je možné si dopsat i další)

- Napěťové úrovně rozhraní 1.65 - 5.5 V

- Sériový port UART (jen linky RxD a TxD) v úrovních daných napětím Vref např. pro komunikaci

s cílovým zařízením

- 3 LED pro indikaci stavů převodníku

- Indikace napájeni z USB (zelená)

- Indikace přítomnosti napětí Vref (modrá)

- Indikace vysíláni a přijímání přes UART (dvojitá červená/zelená)

- Podporováno nástrojem OpenOCD

- Možnost připojení napětí +5V z USB na programovací konektor pro případné napájení cílové aplikace

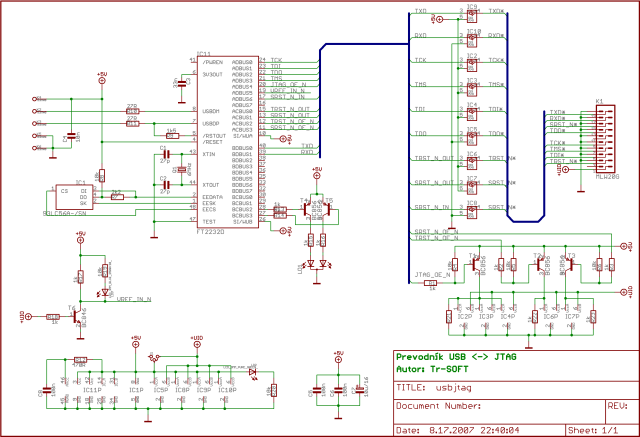

Schéma

DPS

Podklady pro EAGLE 4.16 jsou v download sekci

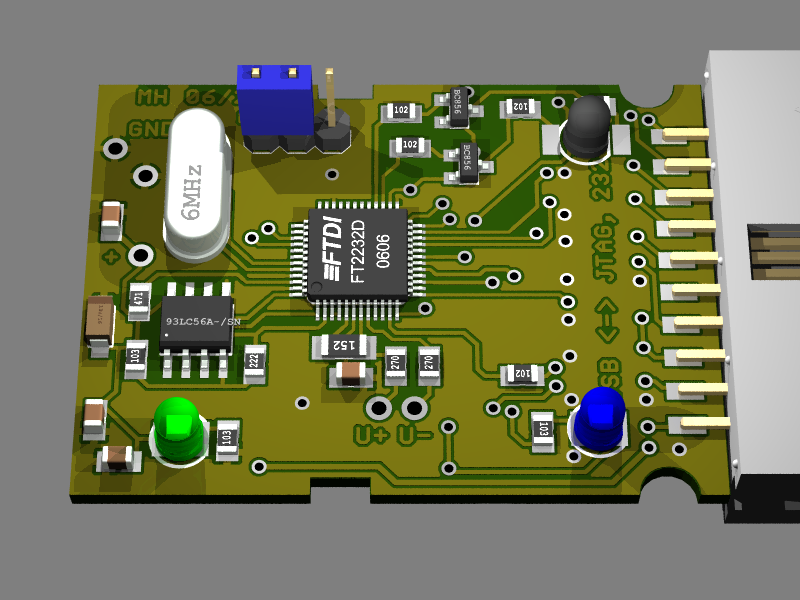

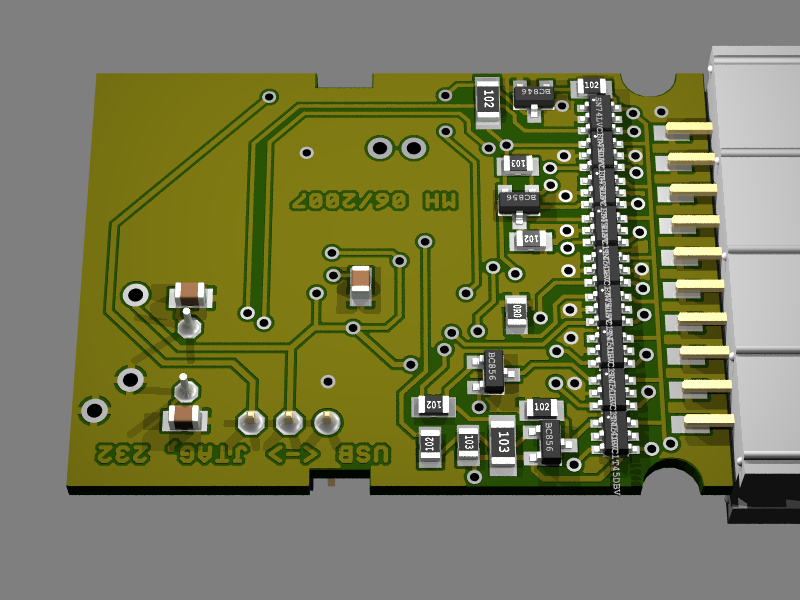

Vyrenderované obrázky DPS

Strana součástek (TOP)

Strana spojů (BOTTOM)

Zapojení JTAG konektoru (na převodníku)

směry přenosu brány z pohledu převodníku

| Vref |

PWR |

1 |

2 |

N.C. |

- |

| TRST_N |

OUT |

3 |

4 |

PWR |

GND |

| TDI |

OUT |

5 |

6 |

PWR |

GND |

| TMS |

OUT |

7 |

8 |

PWR |

GND |

| TCK |

OUT |

9 |

10 |

PWR |

GND |

| - |

N.C. |

11 |

12 |

PWR |

GND |

| TDO |

IN |

13 |

14 |

PWR |

GND |

| SRST_N |

I/O |

15 |

16 |

PWR |

GND |

| RxD |

IN |

17 |

18 |

PWR |

GND |

| TxD |

OUT |

19 |

20 |

PWR |

GND |

Alternativní funkce pinů na JTAG konektoru

| Pin na konektoru |

Pin na FT2232D |

Primární fuknce |

SPI |

I2C |

| 5 |

23 |

TDI |

DIN |

SDA |

| 7 |

21 |

TMS |

CS |

- |

| 9 |

24 |

TCK |

SCK |

SCL |

| 13 |

22 |

TDO |

DOUT |

SDA |

Fotky osazeného převodníku

viz elektro:USB na JTAG:Fotky

Chyby

U DPS revize 1.0 je drobná chyba a to chybějící odpory u výstupních budíčů. Oprava je snadná a to následující, je nutné připjit odpor o hodnotě 1k vždy mezi kolektor tranzistorů T1, T2, T3 a zem (viz foto). U desek revize 1.1 je tato chyba již odstraněna.

|